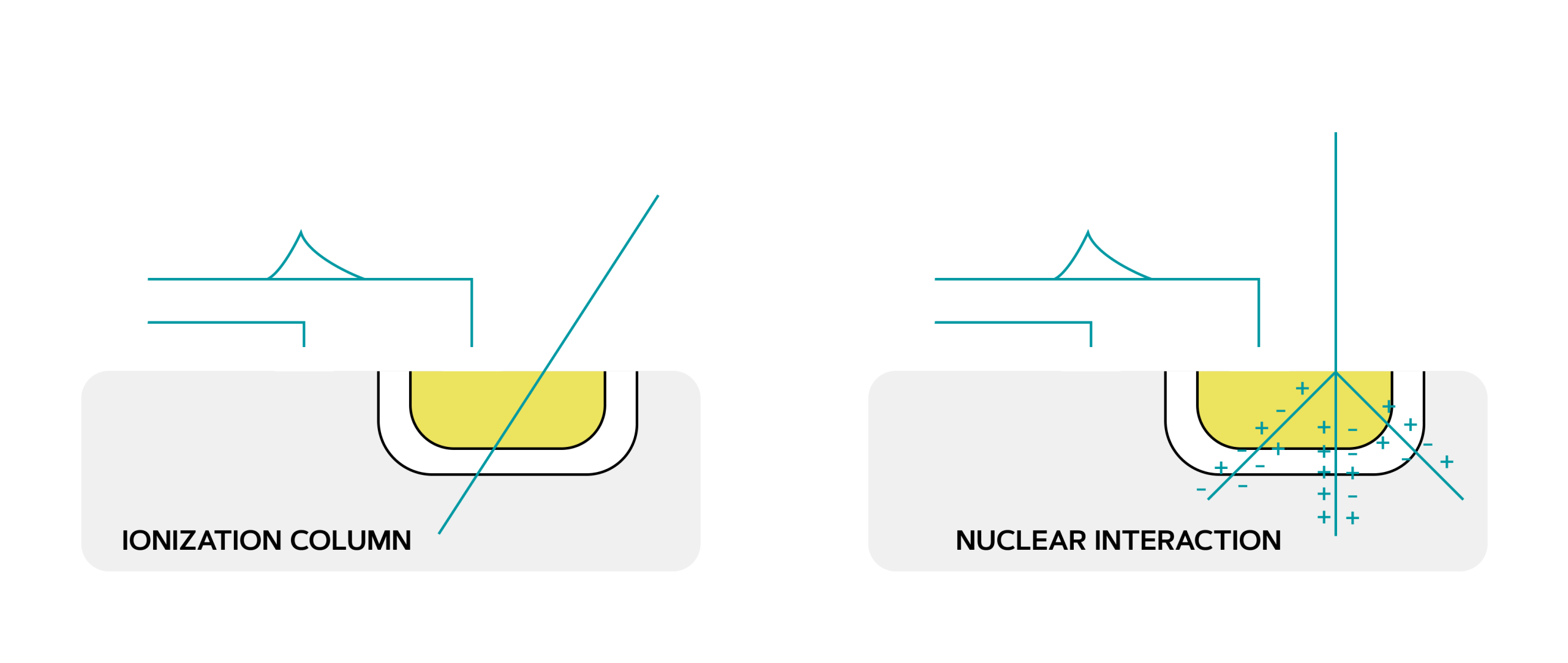

In the world of high-reliability electronics, particularly in aerospace and other critical applications, the impact of radiation on programmable hardware can be a significant concern. Single Event Effects (SEE), caused by charged particles striking sensitive electronic components, can lead to data corruption and system failure. To combat this, designers employ various mitigation techniques, with Triple Modular Redundancy (TMR) serving as a fundamental method for enhancing system reliability.

Understanding Triple Modular Redundancy

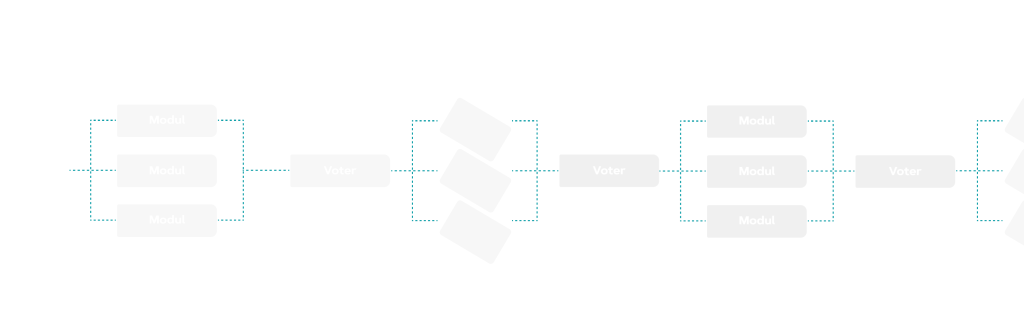

Triple Modular Redundancy is a well-established technique for mitigating Single Event Effects. The core principle lies in spatial redundancy. Instead of having a single functional unit, the logic is triplicated. The outputs of these three identical modules are then fed into a voter circuit. Suppose one of the modules produces an erroneous output due to an SEE. In that case, the voter will be able to correct the fault by taking the majority vote of the three inputs, ensuring the system continues to operate correctly.

This approach is fundamental for critical parts of an FPGA design, such as watchdogs, control logic for essential elements, or even entire IP cores that require the highest level of reliability.

Streamlining TMR implementation with an open-source VHDL library

To simplify and accelerate the process of implementing TMR in VHDL, a library of functions has been developed. This library is designed to speed up the coding process when targeting TMR for the critical sections of your FPGA design.

Currently, the TMR library offers support for AMD FPGAs, with plans to extend compatibility to other vendors in future releases. A key advantage of utilizing this library is the introduction of a USE_TMR generic or package constant. This feature provides the flexibility to enable or disable the TMR functionality. This is incredibly beneficial for the development lifecycle, as it simplifies debugging during the design phase and allows for the creation of both industrial-grade and space-grade IP from the same codebase. The library is written in VHDL-2008.

In-Code spreading of critical elements

An interesting observation when using tools like Vivado is their tendency to group Flip-Flops (FFs) and other FPGA elements as closely as possible to optimize timing performance. While beneficial for speed, this tight clustering makes these groups more susceptible to multiple-bit and cell upsets from a single high-energy particle event.

The traditional method to counteract this involves manually spreading these critical elements in the design constraints file (xdc), a process that is often tedious and cumbersome. To address this, the TMR library is exploring an innovative in-code approach to spread out FFs and Look-Up Tables (LUTs). This is achieved by utilizing the LOC attribute with a seed for the X and Y slice coordinates.

This functionality is still a work in progress, as the number of elements within a single XY_SLICE and the total number of XY slices can vary depending on the specific FPGA family and chip. These variables must be carefully considered for the in-code spreading to be effective and reliable. While several functions are still under development to fully implement this feature, the basic concept has been successfully proven.

Protostar Labs is always open for new collaborations with other companies. If you require expertise in writing code for your next project or need assistance with a complete RTL design, whether it’s for space-grade applications or not, feel free to contact our sales team.